|

|

|

Beide MaÔnahmen erfordern neue und verbesserte

Einzelprozesse. Die dann herstellbaren kleineren Strukturen f■hren zu

neuen Problemen, die wiederum neue Prozesse und Technologien erfordern.

Sieht man von der Lithographie ab, so ergeben sich als platzsparende

MaÔnahmen im wesentlichen vier Prozesskomplexe, die gegen■ber dem

1-MBit-DRAM neu sind.

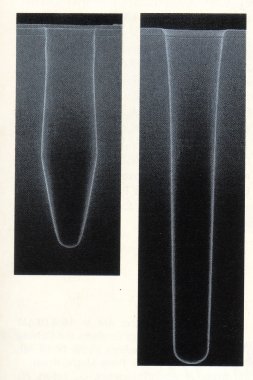

Grabenkondensator

Wie bereits angedeutet, wurde durch Einbeziehung der

dritten Dimension - der 1-MBit-DRAM wurde noch in Planartechnik

hergestellt - eine ausreichende Kondensatorkapazitðt in Form eines

Grabens erreicht. Die technologischen Probleme, die dieser

Grabenkondensator mit sich bringt, sind jedoch beachtlich:

-

átzung der L—cher (Bild 9) - Dotieren der Seitenwðnde

-

Erzeugung des Kondensatordielektrikums

-

Herstellung und Dotierung der Polyelektrode im Graben

-

Auff■llen des Grabens

-

Vermeidung von elektrischen Durchschlðgen zwischen

zwei Grðben

Die Beherrschung allein dieses Prozesskomplexes bedingte

einen Aufwand von rund 100 Mannjahren und etwa 3-4 Jahre intensiver

Arbeit.

Dielektrikum

Um eine gleichmðÔige Dicke des im Gegensatz zum

1-MBit-DRAM dreidimensionalen Kondensatordielektrikums zu erreichen,

wird ein Sandwich aus thermischem Oxid, abgeschiedenem Nitrid und einem

weiteren thermischen Oxid geformt - abgek■rzt ONO. Damit sind die beiden

extrem wichtigen Grenzflðchen zwischen Dielektrikum und Silizium erstmal

unverðndert, gleichzeitig sorgt das gleichmðÔig dicke Nitrid aber f■r

eine verbesserte Durchschlagfestigkeit und erh—hte

Dielektrizitðtskonstante

gleichmðÔiges Dieleektrikum

Éberlappende Bitleitungskontakte

Beim 4-MBit-DRAM wurden durch einen komplizierten

Prozess die Gates der Transistoren in Oxid eingekapselt, die Verbindung

f■r die Bitleitungskontakte kann dann so groÔ sein, dass es die Gates

■berlappt - man spricht von Fully Overlapping Bitlilie Contacts (FOBICs).

Ein Sicherheitsabstand wird nicht mehr ben—tigt, das Bitleitungsraster

kann um etwa 1 çm enger gef■hrt werden. Erkauft wird dieser Platzgewinn

durch etwa 40 zusðtzliche Prozessschritte.

Diffusionsbarriere

Um unerw■nschte Wechselwirkungen etwa metallurgischer

Art zwischen den Aluminium-Leiterbahnen und dem Siliziumsubstrat zu

verhindern, wurde in den Kontakten zwischen Wortleitung und

Steuertransistor (Bild 10) eine Zwischenschicht aus Titan-Nitrid

eingezogen. Obwohl hier im Grunde genommen nur wenige zusðtzliche

Prozessschritte hinzukommen, entstand ein zusðtzlicher Mehraufwand in

H—he von etwa 15-20 Mannjahren.

Kontaktlochabschrðgung

Ohne eine Kontaktlochabschrðgung w■rde beim Aufbringen

des Aluminiums durch Sputterverfahren nicht mehr gen■gend Aluminium an

die Seitenwðnde und auf den Boden des Kontaktlochs gelangen (Bild 10).

Das Abrunden des Kontaktloches stellt einen weiteren, technisch

schwierigen Prozess dar. Wie auch die Titan-Nitrid-Diffusionsbarriere

ist dieser Schritt eine Konsequenz und nicht eine MaÔnahme der

Strukturverkleinerung.

Mit der Verkleinerung der Strukturen werden die Prozesse zunehmend

komplexer. Dar■ber hinaus werden auch R■ckkopplungen der einzelnen

Prozesse auf andere bedeutsam. So kann beispielsweise die Variation

eines bestimmten Einzelprozesses dazu f■hren, dass f■r einen anderen

v—llig verðnderte Voraussetzungen geschaffen werden. Hier setzen dann

die Prozesskontrollen ein. F■r Einzelheiten sei der Leser auf [6]

verwiesen.

Bild 10.

Der Kontakt der Wortleitungen zum

Halbleitermaterial wird in den sogenannten Kontaktl—chern realisiert.

Damit nach dem Sputtern gen■gend Aluminium die Seitenwðnde und den Boden

des Kontaktlochs bedecken, m■ssen die Kontaktl—cher abgeschrðgt werden.

Der helle Aluminiumfleck ist ein durch die Prðparation entstandener

Artefakt. |

|

|

Projektphasen

Von den ersten Entw■rfen bis zum fertigen Massenprodukt liegt ein Zeitraum

von etwa vier Jahren.

In der ersten Phase laufen Vorarbeiten bei Designern und Prozessentwicklern;

aus den technologischen Randbedingungen und M—glichkeiten folgen die ersten

Designregeln. Einige Vorversuche zu prozesstechnischen Fragen und die

Simulation diverser schaltungstechnischer Ansðtze kumulieren nach etwa

einjðhriger Arbeit im First Silicon (Erstes Silizium) eines Testchips.

Dem schlieÔt sich eine Phase an, in der die Design- und Technologiekonzepte

festgelegt werden, von denen allerdings im Einzelfall auch noch abgewichen

werden kann. Die Bem■hungen m■nden nach etwa zwei Jahren in das

First-Silicon-Produktchip. Dieses funktioniert nur eingeschrðnkt, mit an

Sicherheit grenzender Wahrscheinlichkeit aber nicht vollstðndig.

Aus der Analyse der Design-Technologie, der Montageprobleme und

Pr■ftechnikergebnisse resultiert schlieÔlich ein Neudesign. Alternativkonzepte

werden entschieden. Es entstehen Labormuster, die jetzt eingeschrðnkt, das

heiÔt, noch nicht unter allen an ein Massenprodukt zu stellenden Bedingungen,

funktionieren.

Die M■hle wird erneut in Gang geworfen, alles wird nochmals - diesmal unter

verschðrften Bedingungen - optimiert. Es entstehen Vorserienmuster, die dem

endg■ltigen Produkt schon sehr nahe kommen und auch zum Testen an gute Kunden

weitergegeben werden. Bis zu diesem Zeitpunkt sind etwa drei Jahre

verstrichen. AbschlieÔend findet eine Materialschlacht statt. Ziel ist es,

gen■gend funktionsfðhige Chips als Grundlage f■r statistisch fundierte Tests

zu erhalten, um die Zuverlðssigkeit aller technischen Daten f■r mindestens

zehn Jahre garantieren zu k—nnen. Prozesse, Prozesskomplexe und das ganze

Umfeld m■ssen auf Kosten optimiert und die Ausbeute auf mindestens 10 %

stabilisiert werden. Alles mit dem Ziel, die Qualifikation, dass heiÔt die

Produktionsfreigabe durch die Qualitðtsabteilung zu erhalten und damit in die

Fertigungsphase einzutreten. In der Fertigungsphase wird es wiederum einige

Jahre dauern, bis eine Endausbeute von etwa 80 % erreicht wird.

In den vier Jahren bis zum Anwurf der Produktion wurden aber nicht nur die

geschilderten Entwicklungsaufgaben wahrgenommen. In dieser Zeit wurde bereits

eine neue Fabrik zur Herstellung der Chips gebaut und die ersten Schritte in

Richtung auf die nðchste, um den Faktor vier leistungsfðhigere

Speichergeneration gemacht. |

|

Ausblick In den letzten zwei Jahrzehnten

wurde etwa alle drei bis dreieinhalb Jahre eine neue Speichergeneration mit

vierfacher Leistung entwickelt. Die Frage, ob dies auch in Zukunft so

weitergehen wird, lðsst sich aus heutiger Sicht zumindest f■r die nðchsten

f■nf Jahre positiv beantworten [7]. Zwar handelt es sich bei den ersten

64-MBitSpeichern, die 1990 vorgestellt wurden, nur um teilfunktionsfðhige

Prototypen, die mit der f■r die Massenproduktion ungeeigneten

Elektronenstrahllithographie hergestellt wurden. Dennoch d■rfte unter

Weiterentwicklung der jetzigen Fotolithographie-Techniken bis in den Bereich

des tiefen Ultraviolett (Wellenlðngen von weniger als 250 nm) ein

64-MBit-Speicher mit einer Chipflðche von etwa 200 mm2 fertigbar sein. So

schwerwiegend derzeit manche Probleme auch erscheinen m—gen - die bisherige

Erfahrung hat gezeigt, dass mit jeweils relativ konservativer

Fertigungstechnik doch noch jede Speichergeneration nach einigen Jahren auf

eine Endausbeute von ■ber 70 % gebracht werden konnte. Auch von der

Nachfrageseite her erschlieÔt ein 64-MBit-Speicher gen■gend neue Anwendungen,

beispielsweise bei der Verarbeitung hochaufl—sender Farbbilder, um lohnende

Fertigungsvolumina in Aussicht zu stellen.

Sorgen bereiten den Halbleiterproduzenten allerdings die gewaltigen Kosten,

die der Fortschritt auf dem Speichergebiet mit sich bringt - und das alles in

einem Markt, der durch regelmðÔige Preisverfðlle von mehr als einer

Gr—Ôenordnung innerhalb weniger Jahre gekennzeichnet ist! Die Aufwendungen f■r

Forschung und Entwicklung steigen erfahrungsgemðÔ mit jeder Speichergeneration

um etwa 50 %, f■r neue Fertigungsstðtten muss sogar jeweils etwa doppelt so

viel investiert werden. Eine 16MBit-DRAM-Fabrik mit einer Monatsproduktion von

10 Millionen St■ck erfordert heutigen Schðtzungen zufolge ■ber zwei Milliarden

Mark - mit der Aussicht, drei Jahre spðter f■r die 64-MBit-Fabrik dann mehr

als 4 Milliarden aufbringen zu m■ssen ... . Kein Wunder also, dass Kooperation

und Firmenzusammenschl■sse weltweit zunehmen.

Die technischen Grenzen der heutigen Silizium-Mikroelektronik d■rften etwa mit

dem 1-GBit-Speicher erreicht sein. Immer fraglicher wird jedoch, ob alles

entwickelbare auch —konomisch umgesetzt werden kann. Das schon lange

vorhergesagte Ende der optischen Lithographie wird nun beim 256-MBit-DRAM

erwartet. Die R—ntgenlithographie als derzeit aussichtsreichste Nachfolgerin

f■r Massenfertigung von Strukturbreiten unter 0,2 um bedingt aber so

schwerwiegende ánderungen und Mindestinvestitionen, dass die Barriere f■r

Entwicklung und Produktion in heute schwer vorstellbare Dimensionen wðchst. Da

nicht davon ausgegangen werden kann, dass ein GBit-Chip mit einer Flðche von

etwa 500 mm 2 so genau auf 0,05 çm groÔe Defekte kontrolliert werden kann,

dass die ■ber eine Milliarde Speicherzellen fehlerfrei funktionieren, sind

Designs n—tig, die ■ber eingebaute Redundanz fehlertolerant arbeiten. Vieles

was gestern noch Utopie war, ist heute Realitðt. Wer hðtte in den Zeiten der

Kilo-Speicher die Entwicklung der Mega-Generation f■r m—glich gehalten. Auch

der Obergang von der Mega- zur Giga-Generation entspricht einem

Leistungssprung ■ber drei Gr—Ôenordnungen. Teilnehmen an der Olympiade um die

gr—Ôten Spr■nge werden aber nicht nur die Japaner - auch die Europðer sind mit

von der Partie.

Dr. F. S. Becker, Dr. H. F—ll und K Schl■ter |

|

Literatur [1] Becker, F. S.: From 4M

to 16M-DRAM Technology - Present Problems and Coming Challenges". Proceedings

of the IV SB MICRO (1989), S. 125. Porto Alegre, Brasil.

[2] Maes, H. E., Groeseneken, C., Lebon, H., Witters, J.: Trends in

Semiconductor Memories". Microelectronics Journal, Vol. 20, 1-2, S. 9, 1989.

[31 Pribyl, W., Harter, J., M■ller, W.: Four Megabit Dynamic RAM in

Submicron CMOS Technology with a FOBIC Trench Cell". Siemens Forsch. u.

Entwickl. Ber., Band 16, 6, S. 253. Springer, 1987.

[4] Widmann, D., Mader, K, Friedrich, H.: Technologie hochintegrierter

Schaltungen". Springer, 1988.

[5] Mitsuhashi, K, Ohtake, K, Koba, M., Awane, K in: VLSI Science and

Technology", Eds.: Broydo, S., Osborn, C.M. Electrochem. Soc. Proc., Vol 87,

11, S. 557 (1987)

[6} F—ll, H., Becker, F. S.: Industrielle Entwicklung und Fertigung von

Halbleiterbauelementen". Tagungsband Festk—rperforschung f■r die

Informationstechnik" des 2 LIFF vom 5. bis 16. Mðrz, 1990, S. 16.1 bis 16.79.

Institut f■r Festk—rperforschung, KFA J■lich.

[7] Beinvogel, W., M■ller, W.: Advanced Process Features for High Density

DRAMs". Proceedings of Solid State Devices Materials Conference, SSDM, S. 829.

Sendai, Japan, August 1990. |